# [MG2470] Datasheet

(No. ADS0401)

V1.33

The reproduction of this datasheet is NOT allowed without approval of RadioPulse Inc. All information and data contained in this datasheet are subject to change without notice. This publication supersedes and replaces all information previously supplied. RadioPulse Inc. has no responsibility to the consequence of using the patents describes in this document.

# **REVISION HISTORY**

| Version  | Date       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VER.1.0  | 2010.09.30 | First official version 1.0 release                                                                                                                                                                                                                                                                                                                                                                                                             |

| VER.1.1  | 2010.11.05 | <ul> <li>Sec 7.2/7.3/7.4</li> <li>Updated the interrupt &amp; MAC section</li> <li>Removed the timer 2 &amp; 3 section</li> <li>Changed name of some registers</li> </ul>                                                                                                                                                                                                                                                                      |

| VER.1.2  | 2011.01.03 | <ul> <li>Removed the contents related to MG2470-B72 in all sections.</li> <li>Sec 5.9</li> <li>Updated the electrical characteristics of 16MHz RC Oscillator</li> <li>Sec 6</li> <li>Updated typical application circuit in Figure 3 / Table 2.</li> </ul>                                                                                                                                                                                     |

| VER.1.3  | 2011.4.5   | <ul> <li>Sec 4</li> <li>Added the contents related to the TRSW/TRSWB</li> <li>Sec 7.1.4</li> <li>Table 3 is modified.</li> <li>P1SRC_SEL contents added.</li> <li>Power Control SFR contents added.</li> <li>Sec 8.5</li> <li>Renamed the WDT register to WDTCON register.</li> <li>Sec 8.12</li> <li>Figure 17 is modified.</li> <li>Sec 9.2.8</li> <li>Contents modified.</li> <li>TXDA/P1SRC_SEL/MONCON1 registers are modified.</li> </ul> |

| VER.1.31 | 2011.4.20  | <ul> <li>Sec 9.2.2</li> <li>Table 8 is modified</li> <li>Sec 6</li> <li>Figure 3 &amp; Table 2 are modified</li> </ul>                                                                                                                                                                                                                                                                                                                         |

| VER.1.32 | 2011.5.12  | <ul> <li>Sec 4</li> <li>Added descriptions for RF_P, RF_N, P0[6]</li> <li>Sec 5.2</li> <li>Voltage on any digital pin is added.</li> <li>Sec 6</li> <li>Added description for RF_P &amp; RF_N bias condition.</li> <li>Sec 10</li> <li>Added notice for P0[6] in the ISP mode</li> </ul>                                                                                                                                                       |

| VER.1.33 | 2011.6.28  | <ul><li>Sec 5.3</li><li>changed the values</li></ul>                                                                                                                                                                                                                                                                                                                                                                                           |

# **CONTENTS**

| 1. IN  | FRODUCTION                                     | 7  |

|--------|------------------------------------------------|----|

| 1.1.   | APPLICATIONS                                   | 7  |

| 2. KE  | Y FEATURES                                     | 8  |

|        | OCK DIAGRAM                                    |    |

|        | I DESCRIPTION                                  |    |

|        | CTRICAL CHARACTERISTICS                        |    |

| 5. ELE |                                                |    |

| 5.1.   | Absolute Maximum Ratings                       | 15 |

| 5.2.   | RECOMMENDED OPERATING CONDITIONS               | 15 |

| 5.3.   | DC CHARACTERISTICS                             | 15 |

| 5.4.   | Current Consumption and timing characteristics | 16 |

| 5.5.   | RF RECEIVE SECTION                             | 16 |

| 5.6.   | RF Transmit Section                            | 17 |

| 5.7.   | Frequency Synthesizer                          | 18 |

| 5.8.   | 32MHz Crystal Oscillator                       | 18 |

| 5.9.   | 16MHz RC Oscillator                            | 18 |

| 5.10.  | 32kHz RC Oscillator                            | 18 |

| 5.11.  | Temperature Sensor                             | 19 |

| 5.12.  | ADC                                            | 19 |

| 5.13.  | Flash Memory                                   | 19 |

| 5.1    | 3.1. Flash memory characteristics              | 19 |

| 5.1    | 3.2. Flash memory and page size                | 19 |

| 6. REI | FERENCE APPLICATION CIRCUITS                   | 20 |

| 7. MC  | CU SUBSYSTEM                                   | 22 |

| 7.1.   | MEMORY ORGANIZATION                            | 22 |

| 7.1    |                                                |    |

|        | 2. Data Memory                                 |    |

| 7.1    |                                                |    |

| 7.1    | , 3                                            |    |

| 7.2.   |                                                |    |

| 7.2    |                                                |    |

| 7.2    |                                                |    |

| 7.2    | ·                                              |    |

| 7.3.   | RESETS                                         |    |

| 7.4.   | Interrupts                                     |    |

|        |                                                | _  |

|    | 7.4.1.        | Interrupt Sources                                  | 35  |

|----|---------------|----------------------------------------------------|-----|

|    | 7.4.2.        | Interrupt Enable                                   | 36  |

|    | 7.4.3.        | Interrupt Priority                                 | 37  |

| 8. | PERIPH        | ERALS                                              | 40  |

|    | 8.1. CLO      | ck and Reset Controller                            | 40  |

|    |               | JT/OUTPUT PORTS(GPIO)                              |     |

|    | 8.2.1.        | Port Data Registers(SFR area)                      |     |

|    | 8.2.2.        | Port Direction Registers(SFR area)                 |     |

|    | <i>8.2.3.</i> | Port Input Enable Registers (SFR area)             | 47  |

|    | <i>8.2.4.</i> | Port Drive Strength Selection Registers (SFR area) | 48  |

|    | <i>8.2.5.</i> | Port Pull-up/down Control Registers                |     |

|    | 8.3. TIM      | IER 0/1                                            | 49  |

|    | 8.4. PW       | Ms                                                 | 52  |

|    | 8.5. WA       | TCHDOG TIMER                                       | 55  |

|    | 8.6. UAI      | RT 0/1                                             | 56  |

|    | 8.7. SPI      | MASTER/SLAVE                                       | 68  |

|    | 8.8. I2C      | MASTER/SLAVE                                       | 71  |

|    | 8.9. IR(I     | nfra-Red) Modulator                                | 72  |

|    | 8.10. V       | OICE                                               |     |

|    | 8.10.1.       | 125                                                | 75  |

|    | 8.10.2.       | , , , , , , , , , , , , , , , , , , , ,            |     |

|    | 8.10.3.       | VOICE FIFO                                         | 84  |

|    | 8.11. R       | andom Number Generator(RNG)                        | 90  |

|    | 8.12. C       | Quadrature Signal Decoder                          | 91  |

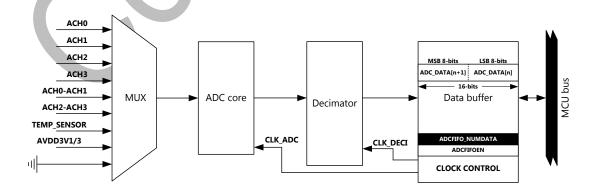

|    | 8.13. A       | DC                                                 | 93  |

|    |               | ower Management                                    |     |

|    | 8.15. S       | LEEP TIMER                                         | 96  |

|    | 8.16.         | 2kHz RC Oscillator                                 | 96  |

|    | 8.17. 1       | 6MHz RC Oscillator                                 | 97  |

|    | 8.18.         | 2MHz Crystal Oscillator                            | 97  |

|    | 8.19. A       | LWAYS-ON REGISTERS                                 | 97  |

| 9. | TRANS         | CEIVER                                             | 102 |

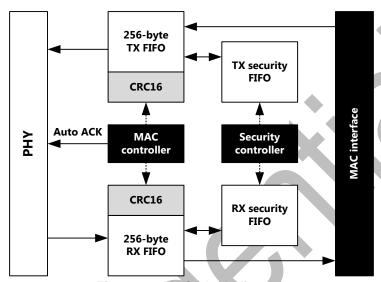

|    | 9.1. MA       | C                                                  | 102 |

|    | 9.1.1.        | Receive Mode                                       | 107 |

|    | 9.1.2.        | Transmit Mode                                      | 109 |

|    | 9.1.3.        | Data Encryption and Decryption                     |     |

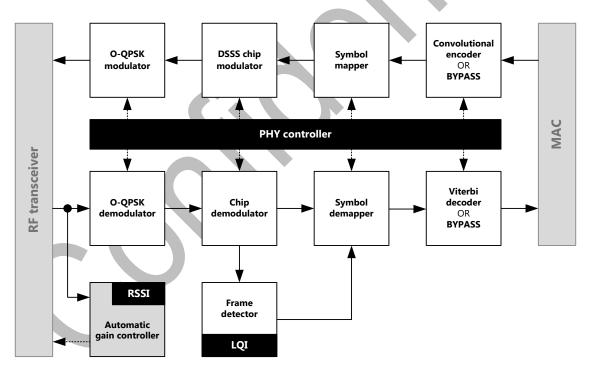

|    | 9.2. PH       | <i>(</i>                                           | 115 |

|    | 9.2.1         | Interrunt                                          | 116 |

| 9.2.2.    | Data Rate                          |     |

|-----------|------------------------------------|-----|

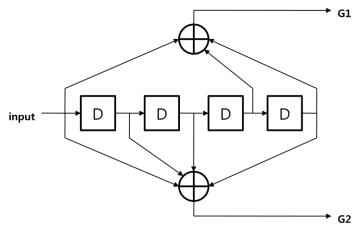

| 9.2.3.    | Forward Error Correction           |     |

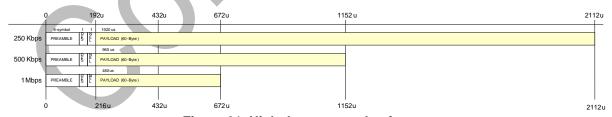

| 9.2.4.    | Packet Format                      | 120 |

| 9.2.5.    | Clear Channel Assessment           | 122 |

| 9.2.6.    | Link Quality Indicator             |     |

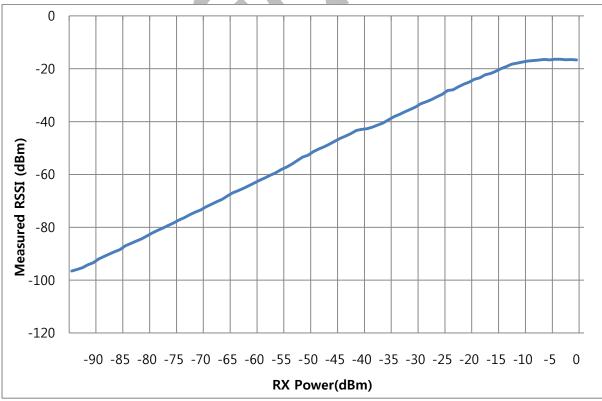

| 9.2.7.    | Received Signal Strength Indicator | 124 |

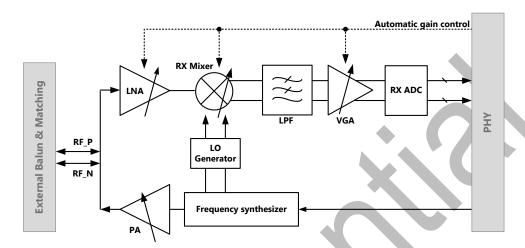

| 9.2.8.    | RADIO                              |     |

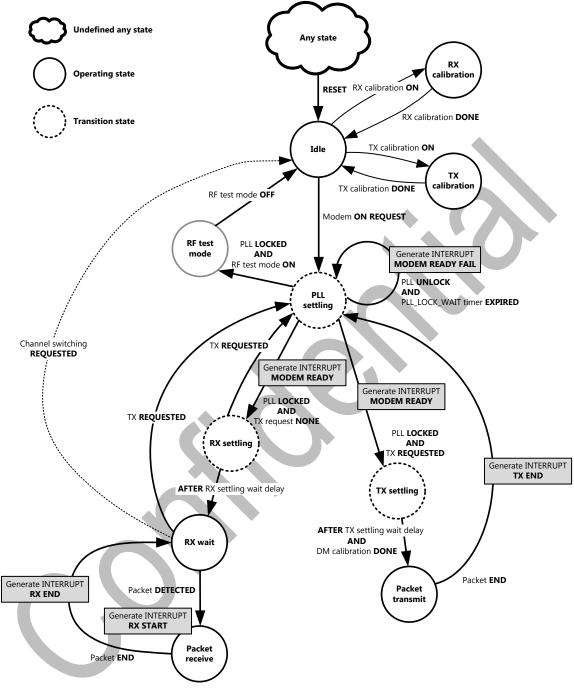

| 9.3. OPE  | rating Modes                       | 127 |

| 10. IN-SY | STEM PROGRAMMING (ISP)             | 129 |

| 11. PACK  | AGE INFORMATION                    | 130 |

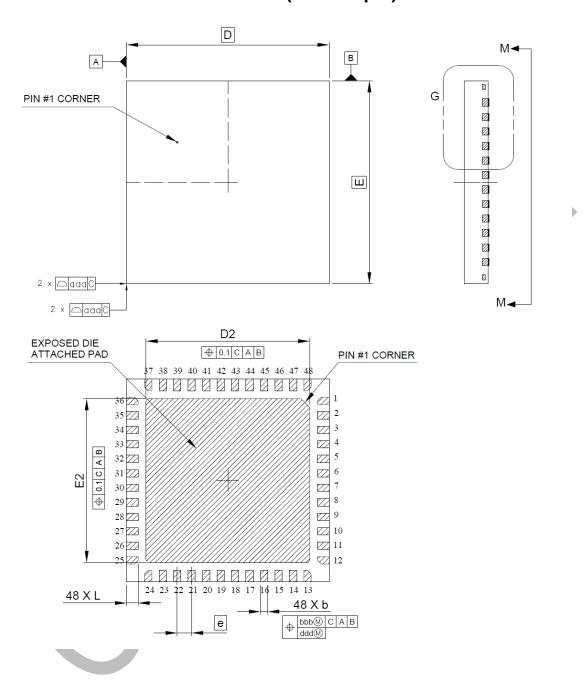

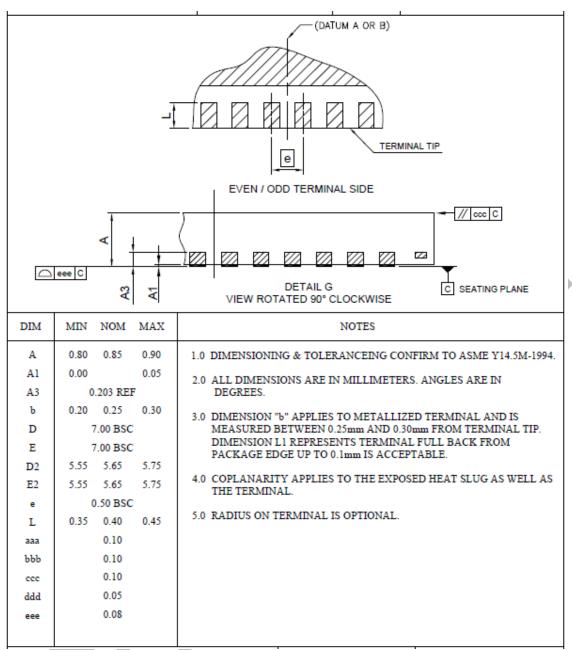

| 11.1. N   | 1G2470-F48 Dimensions (QFN 48-pin) |     |

# **FIGURES**

| FIGURE 1. FUNCTIONAL BLOCK DIAGRAM OF MG2470                        | 10  |

|---------------------------------------------------------------------|-----|

| FIGURE 2. PINOUT TOP VIEW OF MG2470-F48                             | 12  |

| FIGURE 3. MG2470 TYPICAL APPLICATION CIRCUIT                        | 20  |

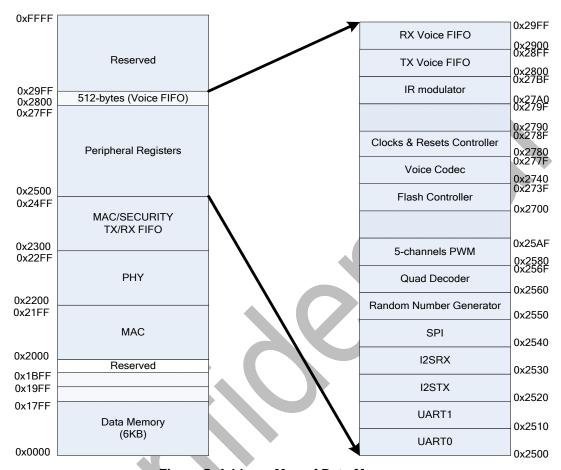

| FIGURE 4. ADDRESS MAP OF PROGRAM MEMORY                             | 22  |

| FIGURE 5. ADDRESS MAP OF DATA MEMORY                                | 23  |

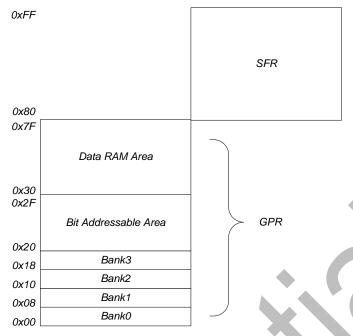

| FIGURE 6. GPRS ADDRESS MAP                                          | 24  |

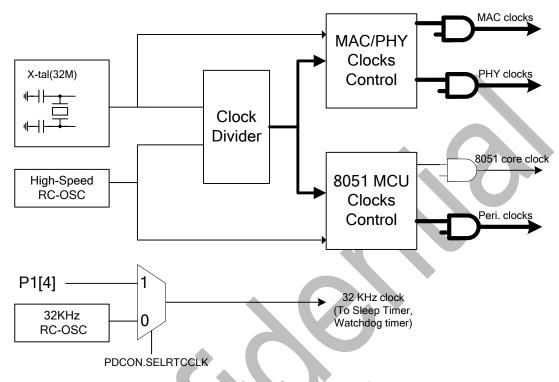

| FIGURE 7. CLOCK SYSTEM OVERVIEW                                     | 29  |

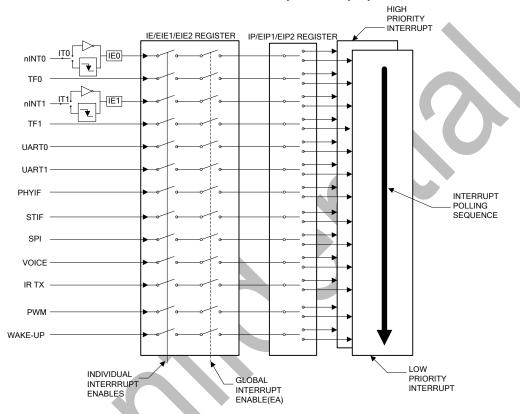

| FIGURE 8. INTERRUPTS OVERVIEW OF MG2470                             | 33  |

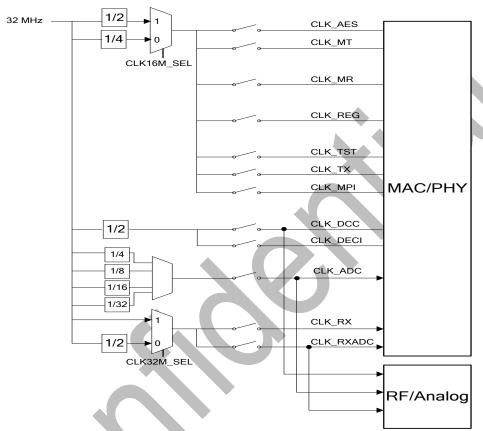

| FIGURE 9. CLOCKS STRUCTURE OF THE MAC/PHY BLOCK                     |     |

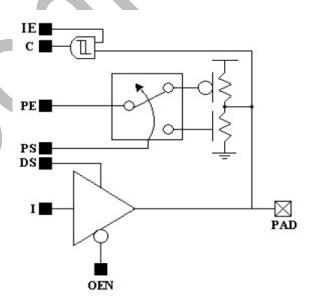

| FIGURE 10. PORT-0/1/3 PAD BLOCK DIAGRAM                             | 45  |

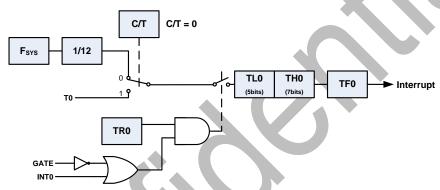

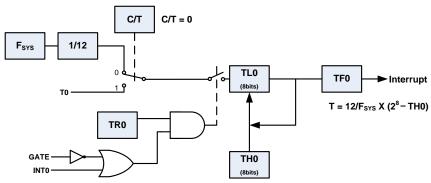

| FIGURE 11. TIMER0 MODE0                                             | 51  |

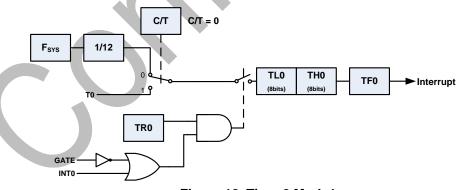

| FIGURE 12. TIMER0 MODE1                                             |     |

| FIGURE 13. TIMER0 MODE2                                             | 52  |

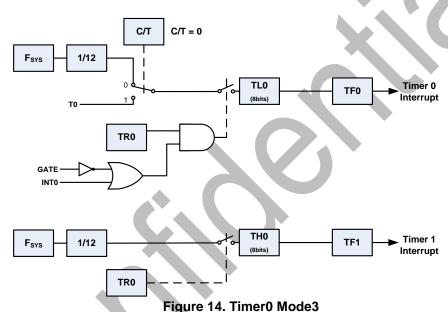

| FIGURE 14. TIMER0 MODE3                                             |     |

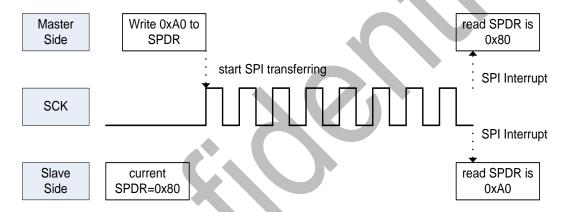

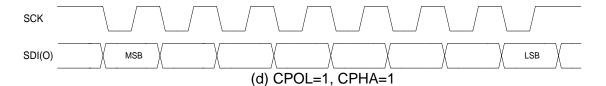

| FIGURE 15. SPI DATA TRANSFER                                        |     |

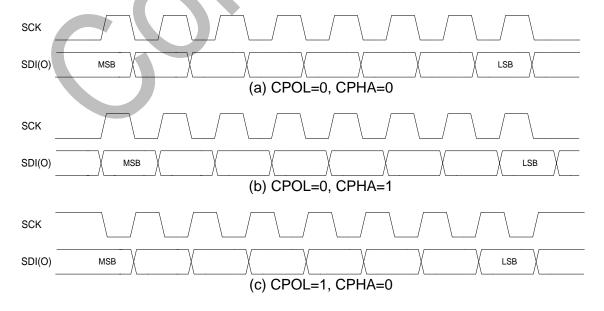

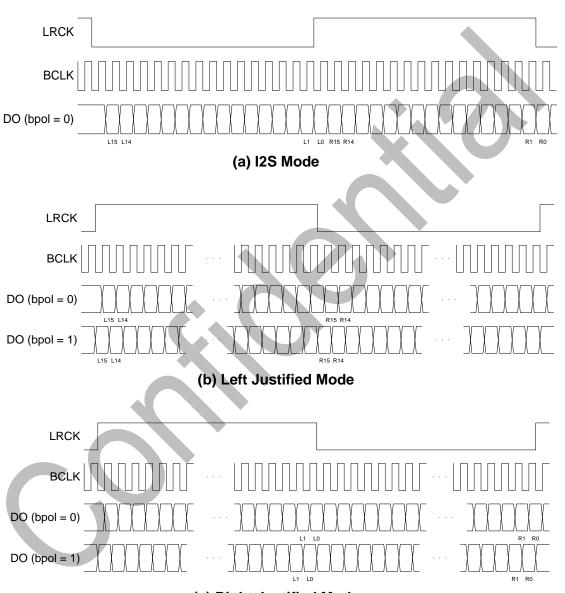

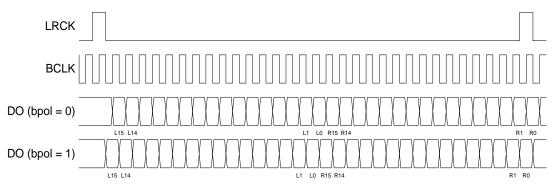

| FIGURE 16. FOUR METHODS IN I2S INTERFACE                            | 77  |

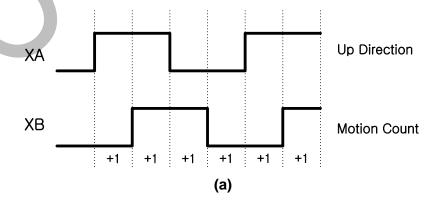

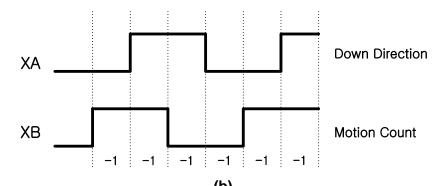

| FIGURE 17. QUADRATURE SIGNAL TIMING BETWEEN XA AND XBX              |     |

| FIGURE 18. MAC BLOCK DIAGRAM                                        |     |

| FIGURE 19. BASEBAND PHY                                             | 115 |

| FIGURE 20. CONVOLUTIONAL ENCODER WITH RATE OF 1/2                   |     |

| FIGURE 21. HIGH DATA RATE PACKET FORMAT                             | 120 |

| FIGURE 22. LOW DATA RATE PACKET FORMAT COMPARED TO THE 250KBPS MODE |     |

| FIGURE 23. MEASURED RSSI (TYPICAL) VERSUS RX INPUT POWER            | 124 |

| FIGURE 24. RF AND ANALOG BLOCK DIAGRAM                              | 125 |

| FIGURE 25 MG2470 STATE TRANSITION DIAGRAM                           | 127 |

| FIGURE 26. PACKAGE DRAWING-QFN48                                    | 131 |

### 1. INTRODUCTION

**MG2470** is a true 2.4 GHz system-on-chip (SOC) designed for low-power and low-cost applications based on IEEE802.15.4 and RF4CE. The MG2470 uses the ISM band of 2.4 ~ 2.48 GHz. In addition to the standard data-rate specified in IEEE802.15.4, enhanced multiple data-rate modes (31.25Kbps ~ 1Mbps) with channel coding are supported.

**MG2470** combines an advanced RF transceiver with an industry-standard enhanced 8051 MCU, a baseband PHY, a MAC with AES-128 HW engine, an in-system programmable 64KB flash memory, a 6-KB RAM, and many other application-specific peripherals. For voice applications, the voice encoder/decoder of ADPCM and  $\mu$ /a-law are embedded. This chip is best for very low-power RF4CE remote control applications.

### 1.1. APPLICATIONS

- 2.4 GHz IEEE 802.15.4 Applications

- RF4CE Remote Control Systems

- Lighting Systems

- Voice Applications

- Home/Building Automation

- Industrial Control and Monitoring

- Energy Management

- Low Power Wireless Sensor Networks

- Consumer Electronics

- Health-care equipments

- Toys

V1.33

### 2. KEY FEATURES

#### **RF Transceiver**

- Single-chip 2.4GHz RF Transceiver

- Low Power Consumption

- High Sensitivity of –99dBm at 250kbps

- No External T/R Switch or Filter needed

- On-chip VCO, LNA, and PA

- Programmable Output Power up to +9.6dBm

- Direct Sequence Spread Spectrum

- O-QPSK Modulation

- Scalable Data Rate including 250Kbps specified in IEEE802.15.4: 31.25Kbps ~ 1Mbps

- RSSI Measurement

- Compliant to IEEE802.15.4

#### **Hardwired MAC**

- Two 256-byte circular FIFOs

- FIFO management

- AES Encryption/Decryption Engine(128 bit)

- CRC-16 Computation and Check

#### 8051-Compatible MCU

- 8051 Compatible (single cycle execution)

- 64KB Embedded Flash Memory

- 6KB Data Memory

- 128-byte CPU dedicated Memory

- 1KB Boot ROM

- Dual DPTR Support

- I2S/PCM Interface with two 256-byte FIFOs

- µ-law/a-law/ADPCM Voice Encoder/Decoder

- Two High-Speed UARTs with Two 16-byte FIFOs(up to 1Mbps)

- Two Timer/Counters

- 5 PWM channels

- Watchdog Timer

- Sleep Timer using the 32kHz RC-OSC clock

- Quadrature Signal Decoder

- 22 General Purpose I/Os for MG2470-F48

- Internal 32kHz RC oscillator for Sleep Timer

- 16 MHz High Speed RC oscillator for the fast start-up from reset & power-down mode

- On-chip Power-on-Reset and Brown-out detector

- 4-channel 12-bit ADC( ENOB > 10-bit)

- SPI Master/Slave Interface with two 16-byte FIFOs

- I2C Master/Slave with 16-byte FIFO

- Programmable IR(Infra-Red) Modulator

- ISP (In System Programming)

- External clock output function(500KHz, 1/2/4/8/16/32 MHz selectable)

### **Clock Inputs**

■ 32MHz Crystal for System Clock

#### **Power**

- 1.8V(Core)/2.0~3.6V(I/O) Operation

- Power Management Scheme with Deep Sleep Mode

- Separate On-chip Regulators for Analog and Digital Circuitry.

- Power Supply Range for Internal Regulator(2.0V(Min) ~ 3.6V(Max))

### **Package**

■ Lead-Free 48-pin QFN Package (7mm x 7mm)

### 3. BLOCK DIAGRAM

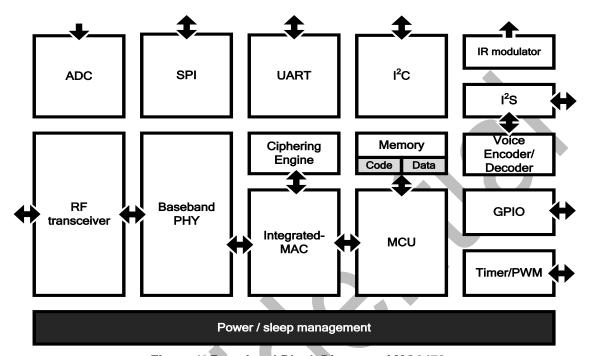

[Figure 1] shows the block diagram of MG2470. The MG2470 consists of a 2.4GHz RF, a baseband PHY, a MAC hardware engine, an industry-standard enhanced 8051 MCU, an insystem programmable flash memory 64KB, a 6KB data RAM, and rich peripherals such as a voice encoder/decoder block, I2C, 5-channel PWM.

Figure 1. Functional Block Diagram of MG2470

MG2470 integrates an RF transceiver compliant to IEEE802.15.4 RF. The RF transceiver operates on an ISM band of 2.4 ~ 2.48GHz with excellent receiver sensitivity and programmable output power up to +9.6dBm. See Sec 9.3 for the detailed explanation for the RF transceiver.

The MAC block supports IEEE802.15.4 compliant functions and it is located between the microprocessor and the baseband modem. MAC block includes FIFOs for transmitting/receiving packets, an AES engine for security operation, a CRC and related control circuit. In addition, it supports automatic CRC check and address decoding.

MG2470 integrates a high performance embedded microcontroller, compatible to an Intel 8051 microcontroller in an instruction level. This embedded microcontroller has 8-bit operation architecture sufficient for controller applications. The embedded microcontroller has 4-stage pipeline architecture to improve the performance over previous compatible chips making it capable of executing simple instructions during a single cycle.

The memory part of the embedded microcontroller consists of program memory and data memory. The data memory has 2 memory areas. For more detailed explanations, refer to Sec 7.1.2. Data Memory.

MG2470 includes 22 GPIOs for MG2470-F48 and various peripheral circuits to aid in the

development of the application circuit with an interrupt handler to control the peripherals. MG2470 uses 32MHz crystal oscillator for RF PLL and 8MHz clock generated from 32MHz in clock generator is used as the default clock of 8051 MCU subsystem. The MAC and clocks of the baseband modem are separately controlled by the system clock and reset module.

MG2470 supports a voice function as follows. The data generated by an external ADC is inputted to the voice block via I2S interface. After the data is received via I2S, it is compressed by the voice encoder and stored in the Voice TXFIFO. Then the data in the Voice TXFIFO is transferred to the MAC TXFIFO and transmitted via PHY. On the other hand, the received data in the MAC RXFIFO is transferred to voice RXFIFO via DMA operation. Then the data in the Voice RXFIFO is decompressed in the internal voice decoder. After that, the decompressed data is transferred to the external DAC via I2S interface.

### 4. PIN DESCRIPTION

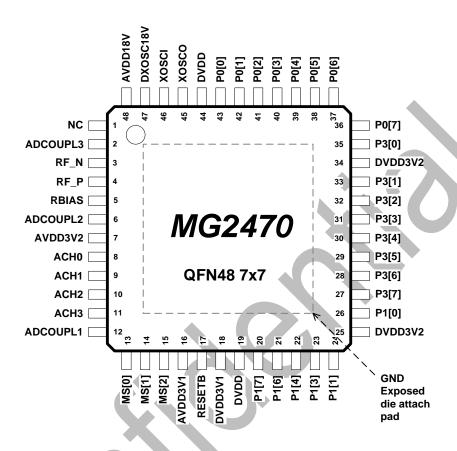

The pin-out diagram of MG2470-F48 is shown in [Figure 2]. The description for that is summarized in [Table 1].

Figure 2. Pinout Top View of MG2470-F48

Note: The exposed ground pad is located at the bottom of the chip and electrically connected to the die ground inside the package. It must be connected to a solid ground plane.

**Table 1. Pin Description**

| Radio, Synth | Radio, Synthesizer, and Oscillator |        |                                                                                                                                                     |  |  |  |

|--------------|------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name         | QFN Pin                            | Туре   | Description                                                                                                                                         |  |  |  |

| AVDD3V1      | 16                                 | Power  | 2.0V to 3.6V RF/Analog power supply connection                                                                                                      |  |  |  |

| AVDD3V2      | 7                                  | Power  | 2.0V to 3.6V RF/Analog power supply connection                                                                                                      |  |  |  |

| ADCOUPL 1    | 12                                 | Power  | 1.8V RF/Analog power supply decoupling. Do not use for supplying external circuits.                                                                 |  |  |  |

| ADCOUPL<br>2 | 6                                  | Power  | 1.8V RF/Analog power supply decoupling. Do not use for supplying external circuits.                                                                 |  |  |  |

| ADCOUPL<br>3 | 2                                  | Power  | 1.8V RF/Analog power supply decoupling. Do not use for supplying external circuits.                                                                 |  |  |  |

| AVDD18V      | 48                                 | Power  | 1.8V RF/Analog power supply connection                                                                                                              |  |  |  |

| RF_P         | 4                                  | RF I/O | Positive RF input signal to LNA in RX mode Positive RF output signal from PA in TX mode It should be biased by ADCOUPL3. Refer to Figure 3 (Sec.6). |  |  |  |

| RF_N         | 3                                  | RF I/O | Negative RF input signal to LNA in RX mode                                                                                                          |  |  |  |

|              |            |                | Negative RF output signal from PA in TX mode It should be biased by ADCOUPL3. Refer to Figure 3 (Sec.6).                                                                                  |

|--------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBIAS        | 5          | Analog<br>I/O  | External precision bias resistor(510kohm) to generate the reference current                                                                                                               |

| ACH0         | 8          | Analog<br>I/O  | ADC input                                                                                                                                                                                 |

| ACH1         | 9          | Analog<br>I/O  | ADC input                                                                                                                                                                                 |

| ACH2         | 10         | Analog<br>I/O  | ADC input                                                                                                                                                                                 |

| ACH3         | 11         | Analog<br>I/O  | ADC input                                                                                                                                                                                 |

| Digital and  | Oscillator |                |                                                                                                                                                                                           |

| Name         | Pin        | Туре           | Description                                                                                                                                                                               |

| DVDD3V1      | 18         | Power          | 2.0V to 3.6V Digital power supply connection                                                                                                                                              |

| DVDD3V2      | 25,34      | Power          | 2.0V to 3.6V Digital power supply connection                                                                                                                                              |

| DVDD         | 19,44      | Power          | 1.8V Digital power supply decoupling. Do not use for supplying external circuits.                                                                                                         |

| DXOSC18<br>V | 47         | Power          | 1.8V Digital power supply connection                                                                                                                                                      |

| RESETB       | 17         | Digital input  | Reset, active low                                                                                                                                                                         |

| MS[0]        | 13         | Digital input  |                                                                                                                                                                                           |

| MS[1]        | 14         | Digital input  | Mode Selection  Value   Mode Configuration                                                                                                                                                |

| MS[2]        | 15         | Digital input  | 000 Normal mode with internal digital regulator 010 Normal mode with external digital regulator 100 ISP mode with internal digital regulator 110 ISP mode with external digital regulator |

| P0[0]        | 43         | Digital<br>I/O | Port P0.0/I2SRX_DI/PWM0, 16mA drive capability                                                                                                                                            |

| P0[1]        | 42         | Digital<br>I/O | Port P0.1/I2SRX_LRCLK/PWM1, 16mA drive capability                                                                                                                                         |

| P0[2]        | 41         | Digital<br>I/O | Port P0.2/I2SRX_BCLK/PWM2, 16mA drive capability                                                                                                                                          |

| P0[3]        | 40         | Digital<br>I/O | Port P0.3/I2SRX_MCLK/PWM3, 16mA drive capability                                                                                                                                          |

| P0[4]        | 39         | Digital<br>I/O | Port P0.4/I2STX_DO/PWM4, 16mA drive capability                                                                                                                                            |

| P0[5]        | 38         | Digital<br>I/O | Port P0.5/I2STX_LRCLK/PTC_GATE0                                                                                                                                                           |

| P0[6]        | 37         | Digital<br>I/O | Port P0.6/I2STX_BCLK/PTC_GATE1  *Notice: This pin should not be set to 0 under the ISP mode.                                                                                              |

| P0[7]        | 36         | Digital<br>I/O | Port P0.7/I2STX_MCLK/PTC_GATE2                                                                                                                                                            |

|                |            |                | <del>-</del>                                         |

|----------------|------------|----------------|------------------------------------------------------|

| P1[0]          | 26         | Digital I/O    | Port P1.0/RXD1                                       |

| P1[1]          | 24         | Digital<br>I/O | Port P1.1/TXD1                                       |

| P1[3]          | 23         | Digital<br>I/O | Port P1.3/QUADZA/PTC_GATE3/IR_TX/CLK_OUT             |

| P1[4]          | 22         | Digital<br>I/O | Port P1.4/QUADZB/EXT_RTC_CLK/PTC_GATE4               |

| P1[6]          | 21         | Digital<br>I/O | Port P1.6/I2C_SCL/TRSWB                              |

| P1[7]          | 20         | Digital<br>I/O | Port P1.7/I2C_SDA/TRSW                               |

| P3[0]          | 35         | Digital<br>I/O | Port P3.0/RXD0/QUADXA                                |

| P3[1]          | 33         | Digital<br>I/O | Port P3.1/TXD0/QUADXB                                |

| P3[2]          | 32         | Digital<br>I/O | Port P3.2/nINT0                                      |

| P3[3]          | 31         | Digital<br>I/O | Port P3.3/nINT1                                      |

| P3[4]          | 30         | Digital<br>I/O | Port P3.4/RTS0/QUADYA/SPIDI/T0                       |

| P3[5]          | 29         | Digital<br>I/O | Port P3.5/CTS0/QUADYB/SPIDO/T1                       |

| P3[6]          | 28         | Digital<br>I/O | Port P3.6/RTS1/SPICLK                                |

| P3[7]          | 27         | Digital I/O    | Port P3.7/CTS1/SPICSN                                |

| XOSCI          | 46         | Analog<br>I/O  | 32MHz crystal oscillator pin                         |

| XOSCO          | 45         | Analog<br>I/O  | 32MHz crystal oscillator pin or external clock input |

| NC             | 1          |                | Do not connect.                                      |

| Ground (M      | G2470-F48) |                |                                                      |

| Exposed bottom | - (        | Ground         | Ground for RF, Analog, digital core, and I/O         |

### 5. ELECTRICAL CHARACTERISTICS

## 5.1. Absolute Maximum Ratings

| Parameter                                                        |         | Min. | Max | Unit |                                                       |

|------------------------------------------------------------------|---------|------|-----|------|-------------------------------------------------------|

| Supply<br>Voltage(AVDD3V1,AVDD3V2<br>,DVDD3V1,DVDD3V2)           |         | -0.3 | 3.6 | V    | All supply pins must have the same voltage.           |

| Core voltage(ADCOUPL1,ADCOU PL2,ADCOUPL3,AVDD18V,D VDD,DXOSC18V) |         | -0.3 | 2   | V    |                                                       |

| Storage Tempe                                                    | erature | -40  | 85  | °C   |                                                       |

| ESD                                                              | HBM     |      | 2   | kV   | All pads, according to human-body model(JEDEC STD 22) |

| ESD                                                              | CDM     |      | 500 | V    | According to charged-device model(JEDEC STD 22)       |

Exceeding one or more of these ratings may cause permanent damage to the device. These are stress ratings only, and the functional operation of the device at these or any other conditions beyond those indicated under "ELECTRICAL SPECIFICATIONS" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

**NOTE1**: These values were obtained under worst-case test conditions specially prepared for the MG2470 and these conditions are not sustained in normal operation environment.

**CAUTION**: ESD sensitive device. Precaution should be used when handling the device to prevent permanent damage.

# 5.2. Recommended Operating Conditions

| Parameter                                                       | MIN  | MAX | UNIT |

|-----------------------------------------------------------------|------|-----|------|

| Operating ambient temperature range, T <sub>OP</sub>            | -40  | 85  | ℃    |

| Operating supply voltage, VDD (AVDD3V1,AVDD3V2,DVDD3V1,DVDD3V2) | 2    | 3.6 | V    |

| Voltage on any digital pin                                      | -0.3 | VDD | V    |

### 5.3. DC Characteristics

T<sub>OP</sub>=25°C, VDD=3.0V, unless otherwise stated.

| Parameter                               | Name | MIN  | TYP | MAX | UNIT |

|-----------------------------------------|------|------|-----|-----|------|

| Logic-low input voltage                 |      | -0.3 |     | 0.8 | V    |

| Logic-high input voltage                |      | 2    |     | VDD | V    |

| I/O-pin pull-up and pull-down resistors |      |      | 48  |     | kΩ   |

| Logic-low output voltage                |      |      |     | 0.4 | V    |

| Logic-high output voltage               |      | 2.4  |     |     | V    |

**NOTE 1:** All voltage values are based on Ground. All input and output voltage levels are TTL-compatible.

# 5.4. Current Consumption and timing characteristics

$T_{OP}$  = 25°C, VDD=3.0V, unless otherwise noted.

| Parameter(Condition)                                                                                                                | MIN | TYP      | MAX | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|------|

| MCU active. No radio and peripherals (UART1&RNG) active.  @ MCU clock = 8MHz                                                        |     | 4.2      |     | mA   |

| RX mode , MCU active and peripherals (UART1&RNG) active                                                                             |     | 25       |     | mA   |

| TX mode , MCU active and peripherals (UART1&RNG) active @maximum output power @+0dBm                                                |     | 43<br>25 |     | mA   |

| Power mode1. Digital regulator on, 16MHz RCOSC and 32MHz crystal oscillator off, 32kHz RCOSC, POR, BOD, and sleep timer active.     |     | 66       |     | μΑ   |

| Power mode1. Digital regulator on, 16MHz RCOSC, 32MHz crystal oscillator, and BOD off, 32kHz RCOSC, POR, and sleep timer active.    |     | 30       | 50  | μΑ   |

| Power mode2. Digital regulator off, 16MHz RCOSC, 32MHz crystal oscillator off, 32kHz RCOSC and sleep timer active.                  |     | 1.25     | 2   | μΑ   |

| Power mode3. Digital regulator off, 16MHz RCOSC, 32MHz crystal oscillator off, 32kHz RCOSC and sleep timer off.                     |     | 0.1      | 1   | μΑ   |

| Wake-up and timing                                                                                                                  |     |          |     |      |

| Power mode1 → MCU Active Digital regulator on, 16MHz RCOSC and 32MHz crystal oscillator off. Start-up of 16MHz RCOSC                |     | 5        |     | μs   |

| Power mode2 → MCU Active Digital regulator off, 16MHz RCOSC and 32MHz crystal oscillator off. Start-up of regulator and 16MHz RCOSC |     | 100      |     | μs   |

| MCU Active → TX or RX Initially running on 16MHz RCOSC, Added start-up time of 32MHz crystal oscillator.                            |     | 992      |     | μs   |

| TX/RX and RX/TX turnaround                                                                                                          |     |          | 192 | μs   |

# 5.5. RF Receive Section

Measured on 4-layer reference design with  $T_{OP}=25^{\circ}C$ , VDD=3.0V, and fc=2450MHz, unless otherwise noted.

| Parameter(Condition)                                    | MIN  | TYP   | MAX  | UNIT  |

|---------------------------------------------------------|------|-------|------|-------|

| RF frequency range                                      | 2394 |       | 2507 | MHz   |

| Maximum input level (PER=1%)                            |      |       |      |       |

| @ 1000kbps                                              |      | -11   |      |       |

| @ 500kbps                                               |      | -12   |      |       |

| @ 250kbps                                               |      | -9    |      | dBm   |

| @ 125kbps                                               |      | -9    |      | ubili |

| @ 62.5kbps                                              |      | -6    |      |       |

| @ 31.25kbps                                             |      | -4    |      |       |

| Spurious radiation                                      |      | -73.7 |      |       |

| @30MHz-1000MHz                                          |      |       |      | dBm   |

| @1GHz-12.75GHz                                          |      | -73.7 |      |       |

| Received RF bandwidth                                   |      | 2     |      | MHz   |

| Channel bandwidth                                       |      | 5     |      | MHz   |

| Receiver sensitivity (PER≤1%, packet length of 22-byte) |      |       |      |       |

| @ 1000kbps                                              |      | -93   |      | dBm   |

| @ 500kbps                                               |      | -94   |      | ubili |

| @ 250kbps                                               |      | -99   |      |       |

| @ 125kbps<br>@ 62.5kbps                                        |   | -100<br>-103 |     |

|----------------------------------------------------------------|---|--------------|-----|

| @ 31.25kbps                                                    |   | -105         |     |

| Adjacent channel rejection (Sensitivity+3, adjacent modulated  |   |              |     |

| channel at ±5MHz, PER=1%, 250kbps)                             |   |              | dB  |

| +5MHz                                                          |   | 30           | ű.D |

| -5MHz                                                          |   | 30           |     |

| Alternate channel rejection (Sensitivity+3, adjacent modulated |   |              |     |

| channel at ±10MHz, PER=1%, 250kbps)                            |   |              | dB  |

| +10MHz                                                         |   | 50<br>50     |     |

| -10MHz                                                         |   | 50           |     |

| Others channel rejection (Sensitivity+3, adjacent modulated    |   |              |     |

| channel at over ±15MHz, PER=1%, 250kbps)                       |   |              | 10  |

| ≥+15MHz                                                        |   | 52           | dB  |

| ≥-15MHz                                                        |   | 54           |     |

| Co-channel rejection (Sensitivity+3. Undesired IEEE 802.15.4   |   |              |     |

| modulated signal at the same frequency. Signal level for       |   | -5.9         | dB  |

| PER=1%, 250kbps)                                               |   |              |     |

| Blocking/desensitization                                       |   | F2           |     |

| +5MHz<br>-5MHz                                                 |   | -53<br>-52   |     |

| +10MHz                                                         |   | -48          |     |

| -10MHz                                                         |   | -46          |     |

| +20MHz                                                         |   | -44          | dBm |

| -20MHz                                                         |   | -40          |     |

| +30MHz                                                         | · | -43          |     |

| -30MHz                                                         |   | -38          |     |

| +50MHz                                                         |   | -41<br>-37   |     |

| -50MHz                                                         |   |              |     |

| RSSI dynamic range                                             |   | 80           | dB  |

| RSSI accuracy                                                  |   | ± 3          | dB  |

# 5.6. RF Transmit Section

Measured on 4-layer reference design with  $T_{\text{OP}}=25^{\circ}\text{C}$ , VDD=3.0V, and fc=2450MHz, unless otherwise noted.

| Parameter(Condition)                                      | MIN  | TYP     | MAX  | UNIT |

|-----------------------------------------------------------|------|---------|------|------|

| RF frequency range                                        | 2394 |         | 2507 | MHz  |

| TX output power (using the recommended matching circuit)  |      |         | 9.6  | dBm  |

| Transmit chip rate                                        |      | 2       |      | Mcps |

| Error vector magnitude(EVM)                               |      | 6.5     |      | %    |

| Harmonics                                                 |      |         |      |      |

| 2 <sup>nd</sup> harmonic                                  |      | -42.5   |      | dBm  |

| 3 <sup>rd</sup> harmonic                                  |      | -77.7   |      |      |

| Spurious emission (complies with EN 300-440, FCC and ARIB |      |         |      |      |

| STD-T66)                                                  |      |         |      |      |

| 30Hz ~ 1GHz                                               |      | < -63.1 |      | dBm  |

| 1GHz ~ 12.75GHz                                           |      | < -42.5 |      |      |

| 5.15GHZ ~ 5.3GHZ                                          |      | < -69.1 |      |      |

### 5.7. Frequency Synthesizer

$T_{\text{OP}}$ =25°C, VDD=3.0V, and fc=2450MHz, unless otherwise noted.

| Parameter(Condition)             | MIN | TYP    | MAX | UNIT   |

|----------------------------------|-----|--------|-----|--------|

| Phase noise, unmodulated carrier |     |        |     |        |

| @ ±100kHz offset                 |     | -79.9  |     |        |

| @ ±1MHz offset                   |     | -104.2 |     | "      |

| @ ±2MHz offset                   |     | -111.0 |     | dBc/Hz |

| @ ±3MHz offset                   |     | -113.8 |     |        |

| @ ±5MHz offset                   |     | -115.6 |     |        |

| Lock time                        |     |        | 192 | μs     |

# 5.8. 32MHz Crystal Oscillator

T<sub>OP</sub>=25°C, DXOSC18V=1.8V, unless otherwise noted.

| Parameter(Condition)                      | MIN | TYP | MAX | UNIT |

|-------------------------------------------|-----|-----|-----|------|

| Crystal frequency                         |     | 32  |     | MHz  |

| Crystal frequency accuracy requirement    | -40 |     | 40  | ppm  |

| Equivalent series resistance(ESR)         |     |     | 60  | Ω    |

| Crystal shunt capacitance(Co)             |     |     | 5   | pF   |

| Crystal load capacitance(C <sub>L</sub> ) |     |     | 16  | pF   |

| Start-up time                             |     |     | 0.8 | ms   |

# 5.9. 16MHz RC Oscillator

T<sub>OP</sub>=25°C, DXOSC18V=1.8V, unless otherwise noted.

| Parameter(Condition)                  | MIN | TYP | MAX | UNIT |

|---------------------------------------|-----|-----|-----|------|

| Frequency                             |     | 16  |     | MHz  |

| Frequency accuracy before calibration | -25 |     | 25  | %    |

| Frequency accuracy after calibration  | -3  |     | 3   | %    |

| Initial calibration time              |     | 50  |     | μs   |

| Start-up time                         |     |     | 1   | μs   |

### 5.10. 32kHz RC Oscillator

$T_{OP}=25$ °C, VDD=3.0V, unless otherwise noted.

| Parameter(Condition)                 | MIN  | TYP    | MAX | UNIT |

|--------------------------------------|------|--------|-----|------|

| Calibrated frequency                 |      | 32.787 |     | kHz  |

| frequency accuracy after calibration | -0.3 |        | 0.3 | %    |

| Initial calibration time             |      | 1      |     | ms   |

| Start-up time                        |      |        | 100 | μs   |

### **5.11. Temperature Sensor**

VDD=3.0V, unless otherwise noted.

| Parameter(Condition)    | MIN | TYP   | MAX | UNIT  |

|-------------------------|-----|-------|-----|-------|

| output voltage at -40°C |     | 716   |     | mV    |

| output voltage at 0°C   |     | 847   |     | mV    |

| output voltage at 40°C  |     | 978   |     | mV    |

| output voltage at 80°C  |     | 1109  |     | mV    |

| temperature coefficient |     | 3.275 |     | mV/°C |

All measurement results are obtained using the 12bit ADC.

### 5.12. ADC

$T_{OP}$ =25°C, VDD=3.0V, unless otherwise noted.

| Parameter(Condition)                                                    | MIN | TYP      | MAX | UNIT |

|-------------------------------------------------------------------------|-----|----------|-----|------|

| Input voltage                                                           | 0   |          | VDD | V    |

| Input resistance                                                        |     | 150      |     | kΩ   |

| Full-scale signal                                                       |     | <b>\</b> | 3   | V    |

| Effective number of bits(ENOB) Single-ended input, 12bit setting        |     | 10.8     |     | bits |

| Signal to noise and distortion(SINAD) Single-ended input, 12bit setting |     | 66.78    |     | dB   |

| Current consumption                                                     |     | 0.62     |     | mA   |

| Internal reference voltage                                              |     | 1.25     |     | V    |

# 5.13. Flash Memory

### 5.13.1. Flash memory characteristics

|                | or o |                                           |        |     |     |        |  |

|----------------|------------------------------------------|-------------------------------------------|--------|-----|-----|--------|--|

| Characteristic | Symbol                                   | Conditions                                | MIN    | TYP | MAX | UNIT   |  |

| Endurance      | Nendu                                    | 20ms erase and 20 us program time at 1.8V | 20,000 |     |     | cycles |  |

| Data retention | Tret                                     | 25 °C                                     | 100    |     |     | years  |  |

# 5.13.2. Flash memory and page size

| Name                    | Size  | Unit  |

|-------------------------|-------|-------|

| Flash main memory block | 65536 | bytes |

| Flash information block | 1024  | bytes |

| Flash page size         | 512   | bytes |

### 6. REFERENCE APPLICATION CIRCUITS

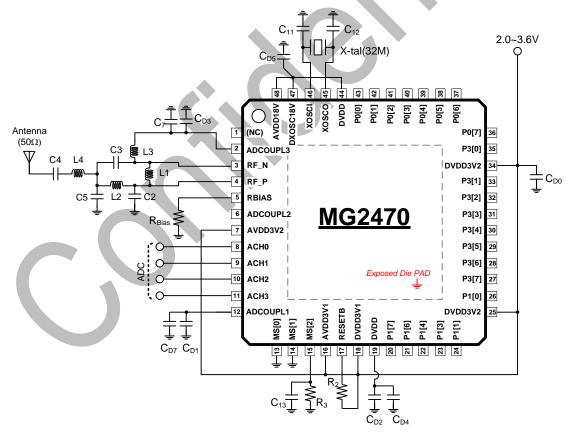

A typical application diagram of the MG2470 is shown in [Figure 3]. Only a few external components are required for the operation of the MG2470. [Table 2] describes the external components including decoupling capacitors.

The inductor, L1 is used as a matching component for the LNA and as an output load for the PA, respectively. The components near the RF\_P/RF\_N pins, L2, L3, C2, and C3 form a balun which converts the differential RF signals to a single-ended RF signal. And, L4, C4, and C5 form a LC harmonic filter to suppress the TX output harmonics. In addition, C4 is needed for DC blocking. All together with adequate values, they also transform the impedance to match a 50-Ohm antenna.

As shown in [Figure 3], RF\_P and RF\_N are biased by ADCOUPL3 through L1 and L3.

The 32MHz crystal provides the reference frequency source for MG2470. C11 and C12 are loading capacitors of it. CD0, CD1, CD2 CD3, CD4, CD5, CD7, and C7 are supply decoupling capacitors, whose values depend on PCB artwork and stack-up information.

The components' values listed in Table 2 are selected for 4-layer reference PCB design.

\*\*\* GND is bottom pad (down-bonding pad) in the above schematic Figure 3. MG2470 Typical Application Circuit

Table 2. Bill of Materials for Figure 3

| No | Component       | Description                                  | Value   |

|----|-----------------|----------------------------------------------|---------|

| 1  | L1              | RF matching inductor                         | 3.3nH   |

| 2  | L2, L3          | RF balun inductors                           | 5.6nH   |

| 3  | C2, C3          | RF balun capacitors                          | 0.75pF  |

| 4  | L4              | RF LC filter/matching inductor               | 3.9nH   |

| 5  | C5              | RF LC filter/matching capacitor              | 1.1pF   |

| 6  | C4              | RF matching/DC blocking capacitor            | 1.8pF   |

| 7  | Rbias           | Resistor for internal bias current reference | 510kohm |

| 8  | X-tal           | 32MHz crystal unit                           | 32MHz   |

| 9  | C11, C12        | Crystal loading capacitors                   | 30pF    |

| 10 | C <sub>D0</sub> | Decoupling capacitor for DVDD3V              | 10uF    |

| 11 | C <sub>D1</sub> | Decoupling capacitor for ADCOUPL1            | 1uF     |

| 12 | C <sub>D7</sub> | Decoupling capacitor for ADCOUPL1            | 1uF     |

| 13 | C <sub>D3</sub> | Decoupling capacitor for ADCOUPL3            | 1uF     |

| 14 | C7              | Decoupling capacitor for ADCOUPL3            | 6pF     |

| 15 | C <sub>D2</sub> | Decoupling capacitor for DVDD                | 1uF     |

| 16 | C <sub>D4</sub> | Decoupling capacitor for DVDD                | 1uF     |

| 17 | C <sub>D5</sub> | Decoupling capacitor for DVDD and DXOSC18V   | 100pF   |

| 18 | R <sub>2</sub>  | Pull-up resistor for RESETB input            | 82kohm  |

| 19 | R <sub>3</sub>  | Pull-down resistor for MS[2] input           | 10kohm  |

| 20 | C <sub>13</sub> | Capacitor for MS[2] input                    | 1uF     |

### 7. MCU SUBSYSTEM

### 7.1. Memory Organization

### 7.1.1. Program Memory

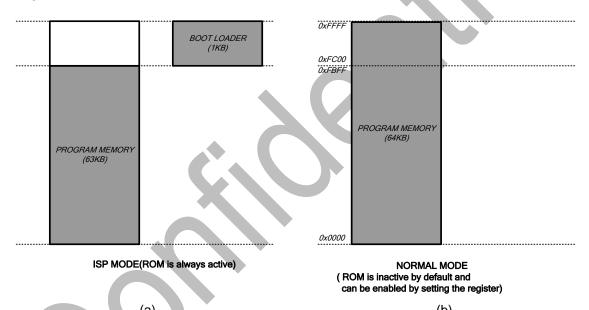

The address space of program memory is 64KB (0x0000~0xFFFF). Basically, the lower 63KB of program memory is implemented by Non-volatile memory. The upper 1KB from 0xFC00 to 0xFFFF is implemented by both Non-volatile memory and ROM. As shown in [Figure 4] below, there are two types of memory in the same address space. The address space, which is implemented by Non-volatile memory, is used as general program memory and the address space, which is implemented by ROM, is used for ISP (In-System Programming).

As shown in (a) of [Figure 4] below, when Power is turned on, the upper 1KB of program memory is mapped to ROM under the ISP mode. As shown in (b) of [Figure 4], this program area (1KB) is used as non-volatile program memory under the normal mode. The ROM area can't be accessed under the normal mode. If necessary, the ROM access is possible by setting the SFR for ENROM. Please see to Sec 7.1.4. WCON SFR for ENROM for details.

### 7.1.2. Data Memory

MG2470 reserves 64 KB data memory address space. This address space can be accessed by MOVX instruction. [Figure 5] shows the address map of MG2470 data memory.

Figure 5. Address Map of Data Memory

The data memory used in the application programs resides in the address range 0x0000-0x17FF. The registers and memory used in the MAC block reside in the address range 0x2000-0x21FF and 0x2300-0x24FF respectively. The registers to control or report the status of PHY block reside in the address range 0x2200-0x22FF.

Registers related to the numerous peripheral functions of the embedded microprocessor reside in the address range of 0x2500-0x29FF.

#### 7.1.3. General Purpose Registers

[Figure 6] describes the address map of the General Purpose Registers (GPRs). GPRs can be addressed either directly or indirectly. As shown in the lower address space of [Figure 6], a bank consists of 8 registers.

The address space above the bank area is the bit addressable area, which is used as a flag by software or by a bit operation. The address space above the bit addressable area includes registers used as a general purpose of a byte unit. For more detailed information, refer to the paragraphs following [Figure 6] below.

Figure 6. GPRs Address Map

**Register Bank 0-3:** It is located from 0x00 to 0x1F (32 bytes). One bank consists of each 8 registers out of 32 registers. Therefore, there are total 4 banks. Each bank should be selected by software as referring the RS field in PSW register. The bank (8 registers) selected by RS value can be accessed by a name (R0-R7) by software. After reset, the default value is set to bank0.

**Bit Addressable Area:** The address is assigned to each bit of 16 bytes (0x20~0x2F) and registers, which is the multiple of 8, in SFR. Each bit can be accessed by the address which is assigned to these bits. 128 bits (16 bytes, 0x20~0x2F) can be accessed by direct addressing for each bit (0x00~0x7F address is assigned) and by a byte unit as using the address from 0x20~0x2F.

Data RAM Area: A user can use the data memory area (0x30~0x7F) as a general purpose.

#### 7.1.4. Special Function Registers(SFR)

The special function registers (SFRs) reside in their associated peripherals or in the 8051 core.

The SFR include the status or control register of the I/O ports, the timer registers, the stack pointers and so on. [Table 3] shows the address to all SFRs in MG2470. Unoccupied locations in the SFR space (the blank locations in Table 3) are unimplemented, i.e., no register exists.

If an instruction attempts to write to an unimplemented SFR location, the instruction executes, but nothing is actually written. If an unimplemented SFR location is read, it returns a zero value.

All SFRs are accessed by a byte unit. However, when SFR address is multiple of 8, it can be accessed by a bit unit.

Table 3. SFR (Special Function Register) Memory Map

| SFR<br>Address | 8 bytes           |                   | it (Opcolai i     |     | ,             | ,   |             |             | SFR<br>Address |

|----------------|-------------------|-------------------|-------------------|-----|---------------|-----|-------------|-------------|----------------|

| 80             | P0                | SP                | DPL               | DPH |               |     |             | PCON        | 87             |

| 88             | TCON              | TMOD              | TL0               | TL1 | TH0           | TH1 | CLKCON<br>1 | CLKCON<br>2 | 8F             |

| 90             | P1                | EXIF1             |                   |     |               |     |             |             | 97             |

| 98             | PERI_CLK_<br>STP0 | PERI_CLK_<br>STP1 | PERI_CLK_<br>STP2 |     | P1SRC_<br>SEL |     |             |             | 9F             |

| A0             |                   |                   | AUXR1             |     |               |     |             |             | A7             |

| A8             | IE                |                   |                   |     |               |     |             |             | AF             |

| В0             | P3                | P00EN             | P10EN             |     | P3OEN         |     |             |             | B7             |

| B8             | IP                | P0_IE             | P1_IE             |     | P3_IE         |     |             |             | BF             |

| C0             | WCON              | P0_DS             | P1_DS             |     | P3_DS         |     |             |             | C7             |

| C8             |                   |                   |                   |     |               |     |             |             | CF             |

| D0             | PSW               |                   | WDTCON            |     |               |     |             |             | D7             |

| D8             | EXIF2             |                   |                   |     |               | X   |             |             | DF             |

| E0             | ACC               |                   |                   |     |               |     |             |             | E7             |

| E8             | EIE1              | EIE2              |                   |     |               |     |             |             | EF             |

| F0             | В                 |                   |                   |     |               |     |             |             | F7             |

| F8             | EIP2              | EIP2              |                   |     |               |     |             |             | FF             |

The following section describes each SFR relating to microprocessor.

| Symbol | Access Mode |  |

|--------|-------------|--|

| RW     | Read/write  |  |

| RO     | Read Only   |  |

| WO     | Write Only  |  |

### WCON (WRITE CONTROL REGISTER, 0xC0)

This register can control the upper 1KB of program memory.

| Bit | Name    | Descriptions                                                                                                                                                                                                                                                                                     | R/W | Reset<br>Value |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| 7:3 |         | Reserved                                                                                                                                                                                                                                                                                         |     | 0              |

| 2   | ISPMODE | ISP Mode Indication. When MS[2:0], an external pin, is '100b', this field is set to 1 by hardware. It notifies the MCU whether ISPMODE or not.                                                                                                                                                   | RO  | -              |

| 1   | ENROM   | When this field is '1', the upper 1KB (0xFC00~0xFFFF) is mapped to ROM. When this field is '0', the upper 1KB (0xFC00~0xFFFF) is mapped to non-volatile memory. The bit setting is effective under the normal mode. In the ISP mode, the ROM is always mapped to address range of 0xFC00~0xFFFF. | R/W | 0              |

| 0   |         | Reserved                                                                                                                                                                                                                                                                                         |     | 0              |

#### **ACCUMULATOR (A or ACC, 0xE0)**

This register is marked as A or ACC and it is related to all the operations.

| Bit | Name | Descriptions | R/W | Reset<br>Value |

|-----|------|--------------|-----|----------------|

| 7:0 | Α    | Accumulator  | R/W | 0x00           |

#### B REGISTER (B, 0xF0)

This register is used for a special purpose when multiplication and division are processed. For other instructions, it can be used as a general-purpose register. After multiplication is processed, this register contains the MSB data and 'A register' contains LSB data for the multiplication result. In division operation, this register stores the value before division (dividend) and the remainder after division. At this time, before division, the divisor should be stored in 'A register' and result value (quotient) is stored in it after division.

| Bit | Name | Descriptions                              | R/W | Reset<br>Value |

|-----|------|-------------------------------------------|-----|----------------|

| 7:0 | В    | B register. Used in MUL/DIV instructions. | R/W | 0x00           |

#### PROGRAM STATUS WORD (PSW, 0xD0)

This register stores the status of the program. The explanation of each bit is as follows.

| Bit   | Name | Descriptions                                   | RW  | Reset |

|-------|------|------------------------------------------------|-----|-------|

| Field |      |                                                |     | Value |

| 7     | CY   | Carry flag                                     | R/W | 0     |

| 6     | AC   | Auxiliary carry flag                           | R/W | 0     |

| 5     | F0   | Flag0. User-defined                            | R/W | 0     |

| 4:3   | RS   | Register bank select.                          | R/W | 0     |

|       |      | 0: Bank0                                       |     |       |

|       |      | 1: Bank1                                       |     |       |

|       |      | 2: Bank2                                       |     |       |

|       |      | 3: Bank3                                       |     |       |

| 2     | OV   | Overflow flag                                  | R/W | 0     |

| 1     | F1   | Flag1. User-defined                            | R/W | 0     |

| 0     | Р    | Parity flag.                                   | R/W | 0     |

|       |      | Set to 1 when the value in accumulator has odd |     |       |

|       |      | number of '1' bits.                            |     |       |

#### STACK POINTER (SP, 0x81)

When PUSH and CALL instructions are executed, some data (like the parameters by function call) are stored in stack to inform the values. In embedded MCU, the data memory area which can be used for a general purpose (0x08~0x7F) is used as a stack area.

This register value is increased before the data is stored and decreased after the data is read when the POP and RET instructions are executed. The default value is 0x07.

| Bit<br>Field | Name | Descriptions  | RW  | Reset<br>Value |

|--------------|------|---------------|-----|----------------|

| 7:0          | SP   | Stack Pointer | R/W | 0x07           |

#### DATA POINTER (DPH: 0x83, DPL: 0x82)

Data pointer consists of a high byte (DPH) and a low byte (DPL) to support 16-bit address. It can be accessed by 16-bit register or by two 8-bit registers respectively.

| Bit<br>Field | Name | Descriptions            | RW  | Reset<br>Value |

|--------------|------|-------------------------|-----|----------------|

| 7:0          | DPH  | Data pointer, high byte | R/W | 0x00           |

| Bit<br>Field | Name | Descriptions           | RW  | Reset<br>Value |

|--------------|------|------------------------|-----|----------------|

| 7:0          | DPL  | Data pointer, low byte | R/W | 0x00           |

### **AUXILIARY CONTROL REGISTER (AUXR1, 0xA2)**

This register is used to implement the Dual DPTR functions. Physically, The DPTR consists of DPTR0 and DPTR1. However, DPTR0 and DPTR1 can be accessed depending on the DPS value of AUXR1 respectively. In other words, they cannot be accessed at the same time.

| Bit   | Name | Descriptions                                                                                                                    | RW | Reset |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------|----|-------|

| Field |      |                                                                                                                                 |    | Value |

| 7:1   |      | Reserved                                                                                                                        |    | 0x00  |

| 0     | DPS  | Dual DPTR Select: Used to select either DPTR0 or DPTR1. When DPS is '0', DPTR0 is selected. When DPS is '1', DPTR1 is selected. | RW | 0     |

#### **GPIO SFRs**

Please refer to Sec 8.2. GPIO for more details. For P1SRC\_SEL, please refer to Sec 9.2.8.

| Register  | Address | Description                              |

|-----------|---------|------------------------------------------|

| P0        | 0x80    | PORT-0 data register                     |

| P1        | 0x90    | PORT-1 data register                     |

| P1SRC_SEL | 0x9C    | PORT-1 source control register           |

| P3        | 0xB0    | PORT-3 data register                     |

| P00EN     | 0xB1    | PORT-0 direction register                |

| P10EN     | 0xB2    | PORT-1 direction register                |

| P3OEN     | 0xB4    | PORT-3 direction register                |

| P0_IE     | 0xB9    | PORT-0 input enable register             |

| P1_IE     | 0xBA    | PORT-1 input enable register             |

| P3_IE     | 0xBC    | PORT-3 input enable register             |

| P0_DS     | 0xC1    | PORT-0 drive strength selection register |

| P1_DS     | 0xC2    | PORT-1drive strength selection register  |

| P3_DS     | 0xC4    | PORT-3 drive strength selection register |

#### WDT (WATCHDOG TIMER) SFR

Please refer to Sec 8.6. WDT for the more details.

| Register | Address | Description                     |

|----------|---------|---------------------------------|

| WDTCON   | 0xD2    | Watchdog timer control register |

#### Timer 0/1 SFRs

Please refer to Sec 8.3. timer 0/1 for the more details.

| Register | Address | Description                      |

|----------|---------|----------------------------------|

| TCON     | 0x88    | Timer/Counter 0 & 1 control      |

| TMOD     | 0x89    | Timer/Counter 0 & 1 mode control |

| TL0      | 0x8A    | Timer/Counter 0 low byte         |

| TH0      | 0x8C    | Timer/Counter 0 high byte        |

| TL1      | 0x8B    | Timer/Counter 1 low byte         |

| TH1 | 0x8D | Timer/Counter 1 high byte |

|-----|------|---------------------------|

|     |      |                           |

### **8051 MCU Clock Control SFRs**

Please refer to Sec 7.2. clock for the more details.

| Register      | Address | Description                             |

|---------------|---------|-----------------------------------------|

| CLKCON1       | 0x8E    | MCU subsystem reference clock control 1 |

| CLKCON2       | 0x8F    | MCU subsystem reference clock control 2 |

| PERI_CLK_STP0 | 0x98    | MCU peripherals clock on/off control 1  |

| PERI_CLK_STP1 | 0x99    | MCU peripherals clock on/off control 2  |

| PERI_CLK_STP2 | 0x9A    | MCU peripherals clock on/off control 3  |

#### **Power Control SFR**

Please refer to Sec 8. power management for the more details.

| Register | Address | Description            |  |

|----------|---------|------------------------|--|

| PCON     | 0x87    | Power control register |  |

| Bit<br>Field | Name | Descriptions                                                                                                            | RW  | Reset<br>Value |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| 7:2          |      | Reserved bits                                                                                                           |     | 0              |

| 1            | PD   | Power-down mode bit 1: start power-down mode 0: clear by hardware when an enabled external interrupt or a reset occurs. | R/W | 0              |

| 0            |      | Reserved bit                                                                                                            |     | 0              |

### 8051 MCU Interrupt SFRs

Please refer to Sec 7.4. interrupt for the more details.

| Register | Address | Description                   |

|----------|---------|-------------------------------|

| IE       | 0xA8    | Interrupt Enable              |

| EIE1     | 0xE8    | Extended Interrupt Enable 1   |

| EIE2     | 0xE9    | Extended Interrupt Enable 2   |

| IP       | 0xB8    | Interrupt Priority            |

| EIP1     | 0xF8    | Extended Interrupt Priority 1 |

| EIP2     | 0xF9    | Extended Interrupt Priority 2 |

| EXIF2    | 0xD8    | Extended Interrupt Flag 2     |

| EXIF1    | 0x91    | Extended Interrupt Flag 1     |

#### 7.2. Clock

The MG2470 supports an advanced and flexible clock selection function to reduce the power consumption depending on the target applications. The clock system overview of MG2470 is shown in the [Figure 7].

Figure 7. Clock System Overview

Two high speed oscillators are included in the MG2470. One is 32 MHz crystal oscillator and the other is high speed RC oscillator (HSRCOSC). The high speed crystal oscillator startup time may be too long for the power critical applications. For example, the wake-up time from the power down mode is longer than the RC oscillator. So, the MG2470 can run on the high speed RCOSC until the crystal oscillator is stable.

#### 7.2.1. 8051 MCU Reference Clock Control

The 8 MHz clock source from 32MHz crystal and a high-speed RC oscillator can be used to drive the internal 8051 MCU clock in MG2470. The default clock frequency of MG2470 is 8 MHz. When selecting 8051 MCU clock, the SFR CLKCON1 should be set as follows;

MCU subsystem Reference Clock Control 1 (CLKCON1, 0x8E)

| Bit<br>Field | Name         | Descriptions | RW  | Reset<br>Value |

|--------------|--------------|--------------|-----|----------------|

| 7            | CLK8M_DIV[2] |              | R/W | 000            |

| 6            | CLK8M_DIV[1] |              |     |                |

| 5   | CLK8M_DIV[0] | Value     | CLK8M divider ratio                |     |        |

|-----|--------------|-----------|------------------------------------|-----|--------|

|     |              | 000       | CLK8M is divided by 1(8MHz)        |     |        |

|     |              | 001       | CLK8M/2(4MHz)                      |     |        |

|     |              | 010       | CLK8M/4(2MHz)                      |     |        |

|     |              | 011       | CLK8M/8(1MHz)                      |     |        |

|     |              | 100       | CLK8M/32(0.25 MHz)                 |     |        |

|     |              | 101       | CLK8M/512(15.625 KHz)              |     |        |

|     |              | 110       | CLK8M/4096(1.953 KHz)              |     |        |

|     |              | 111       | CLK8M/16384(488 Hz)                |     |        |

|     |              |           |                                    |     |        |

|     |              |           |                                    |     |        |

|     |              |           |                                    |     |        |

| 4   | HSRCOSC_SE   | HS RCO    | SC selection                       | R/W | 0      |

|     | L            | 1: the c  | lock selected is the HS RCOSC      |     |        |

|     |              | source    |                                    |     |        |

|     |              | 0: the 8M | 1Hz from 32MHz crystal is selected |     |        |

| 3:0 |              | Reserved  | d bits                             | R/W | 4'b000 |

|     |              | (These    | bits must be set to 4'b0000 for    |     | 0      |

|     |              | normal o  | peration.)                         |     |        |

|     |              |           |                                    |     |        |

MCU subsystem Reference Clock Control 2(CLKCON2, 0x8F)

| Bit<br>Field | Name            | Descriptions                                                                                                                                                                                                                                                         | RW  | Reset<br>Value |

|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| 7            | MCU_INIT_WAI    | This bit is the status flag for detecting the MCU internal clock state change.                                                                                                                                                                                       | R   | 0              |

| 6            | HSRCOSC_ST<br>S | When the MG2470 is gone into the power-down mode, this bit is set to 1. The HS RCOSC source is used as the wake-up clock when exiting from the power-down mode. In order to return to the normal mode, this bit should be cleared by SFR write operation to CLKCON2. | R/W | 0              |

| 5:0          | Reserved        | This value read from this bits is 0                                                                                                                                                                                                                                  | R   | 0              |

The 8051 MCU clock should be changed to normal clock sources after a power-down by SFR CLKCON2 register setting. Please take care of this register setting at wake-up time from a power-down mode.

### 7.2.2. MCU Peripherals Clock Control

The operating clock of 8051 MCU peripherals can be enabled or disabled by some SFR registers write operation. For details, please refer to the SFRs description below.

Peripheral Clock Stop 0(PERI\_CLK\_STP0, 0x98)

| Bit<br>Field | Name     | Descriptions                                                                                         | R/W | Reset<br>Value |

|--------------|----------|------------------------------------------------------------------------------------------------------|-----|----------------|

| 7            | SPI_ON   | This bit is for enabling or disabling the operating clock of SPI.  0 : clock is off  1 : clock is on | R/W | 0              |

| 6            | UART1_ON | This bit is for enabling or disabling the operating clock of UART1.  0: clock is off                 | R/W | 1              |

|   |            | 1 : clock is on                                                                                         |     |    |

|---|------------|---------------------------------------------------------------------------------------------------------|-----|----|

| 5 | UART0_ON   | This bit is for enabling or disabling the operating clock of UART0.  0 : clock is off  1 : clock is on  | R/W | 1  |

| 4 | GPIO_ON    | This bit is for enabling or disabling the operating clock of GPIO.  0 : clock is off  1 : clock is on   | R/W | 1  |

| 3 | PWM_ON     | This bit is for enabling or disabling the operating clock of PWM.  0 : clock is off  1 : clock is on    | R/W | 0  |

| 2 |            | Reserved                                                                                                |     |    |

| 1 | WDT_ON     | This bit is for enabling or disabling the operating clock of WDT.  0: clock is off 1: clock is on       | R/W | 1  |

| 0 | TIMER01_ON | This bit is for enabling or disabling the operating clock of timer 0/1.  0: clock is off 1: clock is on | R/W | /1 |

Peripheral Clock Stop 1(PERI\_CLK\_STP1, 0x99)

| Bit<br>Field | Name      | Descriptions                                                                                                            | R/W | Reset<br>Value |

|--------------|-----------|-------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| 7            | Reserved  |                                                                                                                         | R/W | 0              |

| 6            | IRTX_ON   | This bit is for enabling or disabling the operating clock of IR TX modulator.  0: clock is off  1: clock is on          | R/W | 0              |

| 5            | FLASHC_ON | This bit is for enabling or disabling the operating clock of flash controller.  0: clock is off 1: clock is on          | R/W | 0              |

| 4            | VOICE_ON  | This bit is for enabling or disabling the operating clock of voice block.  0: clock is off  1: clock is on              | R/W | 0              |

| 3            | I2SRX_ON  | This bit is for enabling or disabling the operating clock of I2S RX.  0 : clock is off  1 : clock is on                 | R/W | 0              |

| 2            | I2STX_ON  | This bit is for enabling or disabling the operating clock of I2S TX.  0: clock is off  1: clock is on                   | R/W | 0              |

| 1            | QUAD_ON   | This bit is for enabling or disabling the operating clock of quadrature signal decoder.  0: clock is off 1: clock is on | R/W | 0              |